# RTL2M $\mu$ PATH: Multi- $\mu$ PATH Synthesis with Applications to Hardware Security Verification

Yao Hsiao Stanford University yaohsiao@stanford.edu Nikos Nikoleris Arm Nikos.Nikoleris@arm.com Artem Khyzha Arm Artem.Khyzha@arm.com Dominic P. Mulligan\* Amazon Web Services dominic.p.mulligan@gmail.com

Gustavo Petri\* Amazon Web Services gfpetri@amazon.co.uk

Christopher W. Fletcher University of California, Berkeley cwfletcher@berkeley.edu Caroline Trippel Stanford University trippel@stanford.edu

Abstract—The Check tools automate formal memory consistency model and security verification of processors by analyzing abstract models of microarchitectures, called  $\mu$ SPEC models. Despite the efficacy of this approach, a verification gap between  $\mu$ SPEC models, which must be manually written, and RTL limits the Check tools' broad adoption. Our prior work, called RTL2 $\mu$ SPEC, narrows this gap by automatically synthesizing formally verified  $\mu$ SPEC models from SystemVerilog implementations of simple processors. But, RTL2 $\mu$ SPEC assumes input designs where an instruction (e.g., a load) cannot exhibit more than one microarchitectural execution path ( $\mu$ PATH, e.g., a cache hit or miss path)—its single-execution-path assumption.

In this paper, we first propose an automated approach and tool, called RTL2M $\mu$ PATH, that resolves RTL2 $\mu$ SPEC's singleexecution-path assumption. Given a SystemVerilog processor design, instruction encodings, and modest design metadata, RTL2M $\mu$ PATH finds a complete set of formally verified  $\mu$ PATHs for each instruction. Next, we make an important observation: an instruction that can exhibit more than one  $\mu$ PATH strongly indicates the presence of a microarchitectural side channel in the input design. Based on this observation, we then propose an automated approach and tool, called SYNTHLC, that extends RTL2MµPATH with a symbolic information flow analysis to support synthesizing a variety of formally verified leakage contracts from SystemVerilog processor designs. Leakage contracts are foundational to state-of-the-art defenses against hardware sidechannel attacks. SYNTHLC is the first automated methodology for formally verifying hardware adherence to them.

#### I. INTRODUCTION

A common strategy to improve the efficacy of a formal verification procedure is to analyze an *abstract model* of the target system, which omits irrelevant design details [27], [52], [64]. This approach is exemplified by the *Check* tools [63], which automate formal memory consistency model [55]–[59], [82] and security [80] verification of processors.

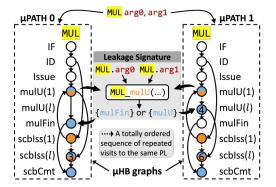

At their core, the Check tools conduct *microarchitectural happens-before* ( $\mu$ HB) analysis [55], which models hardwarespecific program executions as directed  $\mu$ HB graphs (Fig. 1). A node in a  $\mu$ HB graph represents a microarchitectural event, such as a dynamic program instruction (column label) updating a particular set of hardware state elements (row label) [46]. Directed edges denote happens-before relationships [51].

\*Work done while at Arm.

To facilitate  $\mu$ HB analysis, the Check tools analyze a microarchitecture in the guise of an *axiomatic*  $\mu$ SPEC *model*—an abstract model of a microarchitecture, which omits irrelevant RTL details [56]. In particular, a  $\mu$ SPEC model is a set of first-order logic axioms (rules) that describe how to construct  $\mu$ HB graphs to model hardware-specific program executions. Axioms encode (i) all *microarchitectural execution paths* ( $\mu$ PATHS—our term) for each implemented instruction, to instantiate column-wise nodes/edges (as in Fig. 1) and (ii) all possible *microarchitectural dependencies* between pairs of executed instructions, to instantiate edges between columns [46].

Despite finding bugs in real hardware [55], [60], [80]–[82], the *Check* tools have not achieved broad adoption due to a verification gap between  $\mu$ SPEC models, which must be manually written, and RTL.

Our prior work narrows this gap via an automated approach and tool, called RTL2 $\mu$ SPEC, for synthesizing formally verified  $\mu$ SPEC models from simple SystemVerilog processor designs [46]. However, RTL2 $\mu$ SPEC possesses a critical limitation: it cannot discover more than one  $\mu$ PATH per implemented instruction. Hence, designs where instructions may exhibit more than one  $\mu$ PATH are not supported—the *single-execution*path assumption [46]. This restriction is incompatible with pervasive hardware features like: caches, which create hit and miss paths for memory instructions; variable-time functional units (e.g., serial dividers), which create a few to many path possibilities for certain instructions; speculation, which creates commit and squash paths for virtually all instructions; and multiple copies of the same functional unit, where certain instructions may take a path that uses any one of the units. We further show that it precludes designs with microarchitectural side channels, making RTL2 $\mu$ SPEC-synthesized  $\mu$ SPEC models useless for *Check*-based hardware security verification [80].

# A. This Paper

This paper makes three key contributions.

Foundation: Synthesizing Microarchitectural Execution Paths: **Our first contribution** is an automated approach and tool, called RTL2M $\mu$ PATH, that resolves RTL2 $\mu$ SPEC's singleexecution-path assumption. Given a SystemVerilog processor design, instruction encodings, and modest (mostly standard) design metadata, RTL2M $\mu$ PATH uses static netlist analysis, linear temporal logic (LTL) [62], [72] property generation (from property templates), and model checking [15], [28] to find a complete set of formally verified  $\mu$ PATHs ( $\mu$ HB graph columns) for each instruction. Automated  $\mu$ PATH synthesis with RTL2M $\mu$ PATH is enabled by two key aspects of its design.

First, we extend the  $\mu$ HB graph formalism from prior work with *cycle-accurate* timing information. In this paper, a  $\mu$ HB node represents an instruction updating a particular set of hardware state elements *in a specific cycle*; edges encode *onecycle* happens-before relationships. Cycle-accurate  $\mu$ PATHs enable RTL2M $\mu$ PATH to distinguish executions where the same set of state elements is updated a different number of times.

Second, RTL2M $\mu$ PATH recognizes a  $\mu$ HB node during an instruction's execution on a microarchitecture when the instruction *visits* (i.e., *occupies*) a particular *performing location* (PL) in a given cycle. Similar to a pipeline stage, but more granular, a PL represents a *step* of an instruction's execution during which it has exclusive write access to a particular subset of design states. That is, PLs encapsulate instructions' state updates per cycle. We show that PLs are precisely captured by certain finite state machines within a processor's control-path (§III-C). By conceptualizing  $\mu$ HB nodes as instructions' visits to PLs, RTL2M $\mu$ PATH supports speculative, superscalar, and out-of-order pipelines, plus caches.

Observation: Security Implications of  $\mu$ PATH Variability: In designing RTL2M $\mu$ PATH, we make an important observation about how programs leak their private data in hardware sidechannel attacks. Briefly, these attacks are often defined using a telecommunications analogy [48]: a *transmit instruction* (or *transmitter*, in the victim program) modulates a *channel* (hardware resource) in an operand-dependent manner, and a *receiver* (attacker) observes the channel modulation to infer the operand value [48]. We observe that:

**Observation I:** When a transmitter modulates a channel in an operand-dependent manner, it creates operand-dependent  $\mu$ PATH variability (>1  $\mu$ PATH) for one or more *transponder instructions* (or *transponders*—our term). A receiver observes a transmitter's distinct channel modulations as distinct  $\mu$ PATHs for transponder(s).

As an example, consider Fig. 1, which shows two  $\mu$ PATHs for a 32-bit multiply (MUL) instruction executing on CVA6-MUL, a variant of the RISC-V CVA6 CPU [100] that implements the *zero-skip multiply* optimization [10], [12], [40]. On this design, a MUL will spend one cycle in the multiplication unit if it has at least one zero operand; else, it will spend four cycles [12]. Such a MUL is a transmitter [88]: it occupies a hardware resource for an operand-dependent number of cycles.

Clearly, a MUL creates  $\mu$ PATH variability for itself: it may visit mulU, the *multiplication unit* PL, for one ( $\mu$ PATH 0) or four ( $\mu$ PATH 1) consecutive cycles. More subtly, a MUL may create multiple  $\mu$ PATHs for subsequent (in program order), concurrently in-flight instructions, which may stall behind the MUL for one to five cycles before committing (after completing). So, MUL transmitters implicate themselves *and* younger,

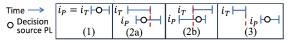

Fig. 1: Two  $\mu$ PATHs for MUL on CVA6-MUL (§I-A) and a leakage signature, which defines transponder MUL's  $\mu$ PATH variability as a function of its own operands following its visit to the mulU PL. Row(1/l): 1st/l-th visit to Row. Node label: value of l for the  $\mu$ PATH.

concurrent instructions as transponders. A receiver observes a MUL's distinct channel modulations as distinct  $\mu$ PATHs (e.g., with distinct latencies) for any of its transponders.

Observation I captures all instances of operand-dependent hardware resource usage (\$V-C2), including prior notions such as *implicit branches* [99], e.g., conditional cache accesses for loads ( $\mu$ PATH variability) that arise due to store and load address-dependent store-to-load forwarding. Thus, **our second contribution** is augmenting the aforementioned telecommunications analogy with the notion of a transponder.

*Application: Synthesizing Leakage Contracts:* Observation I also inspires **our third contribution**: an open-source [1] automated approach and tool, called SYNTHLC, which extends RTL2MµPATH with a symbolic information flow analysis to support synthesizing *a variety of* formally verified microarchitectural *leakage contracts* from SystemVerilog processor designs. Leakage contracts are foundational to hardware sidechannel defenses, implemented in software [25], [35], [67], [68], [87], [101] or hardware [16], [20], [26], [53], [76], [97]–[99]. SYNTHLC is the *first automated methodology* for formally verifying hardware adherence to them.

Specifically, SYNTHLC synthesizes a complete set of formally verified microarchitectural *leakage signatures* from processor RTL. Leakage signatures are a novel formalism that we introduce to capture all relevant features of state-of-the-art leakage contracts, which are not already captured by  $\mu$ PATHs. They are effectively function signatures, which characterize how one or more transmitters create operand-dependent  $\mu$ PATH variability for a transponder with respect to (i.e., following) some step (PL) of the transponder's execution. Fig. 1 depicts a leakage signature, which defines how a MUL transmitter creates  $\mu$ PATH variability for itself (it is also a transponder) as a function of its operands, following its mulU execution step.

From  $\mu$ PATHs and leakage signatures, a variety of formally verified leakage contracts can be easily derived. The canonical *constant-time (CT) contract*, which enumerates a microarchitecture's transmitters and their unsafe operands [3], [11], [47], is captured by the inputs to the leakage signature in Fig. 1.

Overall, SYNTHLC supports synthesizing six different leakage contracts from SystemVerilog processor designs (Table I): CT contracts plus five bespoke leakage contracts from the literature. Collectively, these contracts support two software defenses—the *CT programming defense* [25], [35] and the speculative constant-time (SCT) programming defense [67], [68], [87], [101]—and eight hardware defenses [16], [20], [26], [53], [76], [97]–[99] against hardware side-channel attacks.

*Case Study: Deploying* SYNTHLC *on a Processor Core and Cache:* We deploy SYNTHLC on the RISC-V CVA6 core [100], surfacing 94 unique leakage signatures, 72 transponders, and 26 transmitters. Compared to prior work that analyzes the same design [31], [32], SYNTHLC finds a novel channel that leaks store and load address operands.

We separately deploy SYNTHLC on the CVA6 L1 data cache and cache controller, making it the first leakage contract verification procedure to analyze a realistic processor cache. Beyond uncovering various hardware side channels, our cache experiment showcases the performance and scalability benefits of converting SYNTHLC into a modular procedure.

#### II. BACKGROUND

This section gives an informal overview of hardware sidechannel attacks ( $\Pi$ -A) and defenses ( $\Pi$ -B), including descriptions of six leakage contracts whose implementation in hardware can be formally verified with SYNTHLC.

#### A. Hardware Side-Channel Attacks

In this paper, we study hardware side-channel attacks where a *transmit instruction* (or *transmitter*, in the victim program) modulates a *channel* (hardware resource) in an operand-dependent manner, and a *receiver* (attacker) observes the channel modulation to infer the operand value [48]. We highlight standard assumptions for channels and receivers below.

*Characterizing Channels:* Many hardware resources have been implicated as channels, e.g., caches [70], [95], [96], branch predictors [8], [37], functional units [10], [40], memory ports [9], and more [39], [65], [71], [88]–[90], [93], [94]. Owing to the circumstantial nature of leakage due to particular channels [4], [30], prior work informally classifies them as *stateless* or *stateful* [4]. Stateless channel modulations are observable only in very narrow, specific time windows, usually requiring the receiver to be running at the same time as the victim, e.g., a victim may create memory port contention for a receiver during a victim memory access. Stateful channels may be observed long after they are modulated, e.g., a victim cache access may create a cache miss for a receiver far in the future. We refer to stateless/stateful channels as *dynamic/static* to denote formal definitions that we introduce (§IV-C).

*Receiver Assumptions:* Hardware side-channel attacks and defenses are studied under specific *receiver assumptions*, consisting of an *observer model* and *attacker strategy*.

An observer model defines how channel modulations manifest as observations for a specific receiver. Informally, they may be perceived via their (measurable) effects on certain nondeterministic aspects of program execution, e.g., execution time [18], [41], [70], resource contention [8]–[10], [39], [65], [71], [93], and so on [14], [44], [50], [61], [74], [84].

An attacker strategy specifies whether the receiver may *passively* or *actively* monitor victim channel modulations [19], [30], [79], [88]. In a passive attack, the receiver monitors victim channel modulations without explicitly interfering with the victim's execution, e.g., by measuring victim execution time. In an active attack, the receiver explicitly interacts with the channel modulated by the victim, e.g., by priming and probing shared cache state. The notion of a transponder enables defining both strategies formally (§IV-C).

# B. Hardware Side-Channel Defenses & Leakage Contracts

The goal of a hardware side-channel defense is to ensure that a specific victim program running on a particular microarchitecture will not leak its private data to some receiver via hardware side channels. Towards this goal, state-of-the-art defenses assume the availability of microarchitectural *leakage contracts*, which characterize implementations' transmitters.

The Canonical Leakage Contract: The most widelyadopted leakage contract, the constant-time (CT) contract, enumerates a microarchitecture's transmitters and their unsafe ("leaky") operands. Nascent ISA leakage contracts fall into this category [3], [11], [47]. Given a CT contract, a hardware side-channel defense can ensure that secrets never reach the unsafe operands of transmitters when programs execute. This strategy is embodied in the CT programming defense [25], [35], the gold standard software defense for protecting the architectural executions of cryptopgraphic code [29], [69], [83], [102] from hardware side-channel attacks. Some software [67], [68], [87], [101] and hardware [16], [76] defenses against transient execution attacks-which exploit hardware faults and mis-predictions to steer secrets towards the unsafe operands of transient (bound-to-squash) transmitters [23], [49]-extend this strategy to target programs' speculative executions as well. We refer to software variants of such defenses as speculative constant-time (SCT) programming defenses [87].

*Five Bespoke Leakage Contracts:* Today, the most performant defenses against transient execution attacks are implemented in hardware [20], [26], [53], [97]–[99]. Instead of CT contracts [20], [98], [99] (or in addition to them [26], [53], [97]), these defenses adopt bespoke leakage contracts that are much finer grained. We consider five such fine-grained leakage contracts in this paper. Table I in §IV shows how features of these five contracts, described below for each of the six hardware defenses they enable, and the CT contract map onto the various components of our proposed leakage signatures.

MI6 [20] defends enclaves from hardware side-channel attacks via two mechanisms. First, it requires identifying *dynamic (stateless—§II-A) channels* that arise due to transmitter operand-dependent hardware *resource contention*. Data-independent scheduling logic is implemented for impacted resources. Second, it requires identifying *static (stateful) channels* in order to implement a purge instruction, which flushes relevant microarchitectural states, and partitioning schemes.

OISA [97] attaches secrecy labels to architectural state and detects if a transmitter's unsafe operand, as defined in a CT contract, is ever passed secret data at runtime. It enables transmitters that exhibit execution variability due to *input-dependent arithmetic units* (like MUL in §I-A) to safely process secrets as follows. First, the designer identifies arithmetic units that may be occupied by a transmitter for an operand-dependent number of cycles. Second, control logic is added to enforce operand-independent execution for the unit whenever a transmitter arrives with a secret-labeled unsafe operand.

STT [99] requires identifying all channels and classifying them as explicit channels and implicit channels. Explicit and implicit channels, respectively, arise when transmitters' operand-dependent hardware resource usage affects their own execution behavior and the execution behavior of other instructions. Transmitters that modulate explicit channels are not permitted to execute with (potentially) secret operands. To block implicit channels, designers must also identify explicit branches or implicit branches. Explicit branches are architectural control-flow instructions, like conditional branches. Implicit branches are instructions whose execution behavior depends on the operands of other transmitters. Finally, implicit channels are categorized as prediction-based or resolutionbased. To block prediction-based and resolution-based channels, respectively, the designer must identify predictor structures that are updated by explicit or implicit branches and the points at which these branches resolve their predictions.

SDO [98] extends STT by optimizing its explicit channel defense. First, the designer identifies transmitters that modulate explicit channels. To enable safe speculative execution of these transmitters with (potentially) secret operands, the designer creates a number of data-independent execution path variants for each. These so-called *data-oblivious variants* are derived from the set of realizable microarchitectural execution paths for each transmitter on the baseline design. Then, the designer adds control logic to select which path a transmitter should take based on public predictor state.

Dolma [53] requires a CT contract to delay the execution of transmitters until they become non-speculative. To improve performance, Dolma has several additional requirements. First, the designer must identify *variable-time micro-ops* and any *contention-based dynamic channels* they create. Second, *inducive micro-ops* that exhibit execution variation as a function of *resolvent micro-ops*' (transmitters') operands must be flagged, along with the *prediction resolution point* during the inducive micro-op's execution at which this variation arises. Lastly, *persistent state modifying micro-ops* (transmitters that modulate static channels) must be identified and their persistent state updates delayed until they become non-speculative.

SPT [26] and STT have the same fine-grained leakage contract and differ only in their policy for when it safe to declassify (mark public) data. STT declassifies data once it is not a function of speculatively accessed data. SPT declassifies data once it is inevitable that it will be, or has been, transmitted architecturally; so, SPT additionally requires a CT contract.

# III. RTL2MµPATH APPROACH: FORMALIZING MICROARCHITECTURAL EXECUTION PATHS

Our first contribution is an automated approach and tool, called RTL2M $\mu$ PATH,<sup>1</sup> for uncovering a complete set of formally verified *microarchitectural execution paths* ( $\mu$ PATHs) for each instruction implemented on a SystemVerilog processor design. In this section, we explain the two key technical advances that enable such an analysis: an extension to the  $\mu$ HB graph formalism from prior work (§III-B) and a novel mapping of  $\mu$ HB nodes onto RTL signals (§III-C). We establish the need for both with a motivating example (§III-A). A discussion of RTL2M $\mu$ PATH's implementation details is deferred until §V.

# A. Motivating Example: Operand Packing

Consider an extension to the RISC-V CVA6 CPU [100] that we verify in §VI, called CVA6-OP. The baseline CVA6 design may fetch up to two compressed instructions or one uncompressed instruction per cycle, but only one instruction can be sent to decode per cycle. CVA6-OP is identical to CVA6, except that the ALU has been modified to support *operand packing* [21], and up to *two* instructions can be sent to decode per cycle. In particular, if a pair of (concurrently) decoded instructions perform identical ALU operations *and* feature narrow width operands (32 bits or less, i.e., the upper halves of their 64-bit operation and executed together.

Suppose we want to formally evaluate the vulnerability of CVA6-OP to hardware side-channel attacks with the *Check* tools (i.e., with *CheckMate* [80]). As discussed in §I, we first need to acquire an abstract axiomatic model of the microarchitecture, called a  $\mu$ SPEC model.

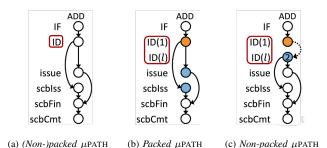

The enabler for *Check*-based hardware security verification is the fact that  $\mu$ SPEC models define how instructions may exhibit variable hardware resource usage when they run on a specific hardware implementation (e.g., a load may experience a cache hit or miss [80]). That is, they specify the various *microarchitectural execution paths* ( $\mu$ PATHs—our term) that may be exhibited by each instruction type (e.g., a LD, MUL, ADD, etc.) on the design. A  $\mu$ SPEC model encodes distinct  $\mu$ PATHs as distinct *microarchitectural happens-before* ( $\mu$ HB) graphs (Fig. 2). A node in a  $\mu$ HB graph represents a microarchitectural event, such as a dynamic program instruction (column label) updating a particular set of hardware state elements (row label) during its execution [46]. Directed edges denote happensbefore relationships [51].

A  $\mu$ SPEC model for CVA6-OP *should* capture the fact that ADDs may exhibit two distinct  $\mu$ PATHs, depending on whether they are packed or not. However, prior work [55]–[59], [80], [82] would represent both of these scenarios with the same  $\mu$ PATH—the one in Fig. 2a. This is because the packed versus unpacked  $\mu$ PATHs differ according to how long an ADD spends in the decode stage (one or two cycles), i.e., how many times the ID node appears. The  $\mu$ HB formalism has not been used to express repeated instances of the same  $\mu$ HB node.

<sup>&</sup>lt;sup>1</sup>"RTL2M $\mu$ PATH" indicates that it finds *multiple* (M)  $\mu$ PATHs per instruction.

Fig. 2: ADD  $\mu$ PATHs on CVA6-OP (§III), using standard  $\mu$ HB graphs from prior work (a) and our new cycle-accurate  $\mu$ HB graphs (b, c). Row(1/*l*): 1st/*l*-th visit to Row. Node label: value of *l* for  $\mu$ PATH.

Even if we resolve this minor modeling issue, the only approach and tool for synthesizing formally verified  $\mu$ SPEC models from processor RTL, called RTL2 $\mu$ SPEC, cannot uncover more than one  $\mu$ PATH per implemented instruction (§I). Beyond missing repeated instances of the same node, RTL2 $\mu$ SPEC's mapping of  $\mu$ HB nodes to RTL signals precludes identifying nodes that appear in some  $\mu$ PATHs but not others. We address these limitations in §III-B and §III-C, respectively.

# B. Extending µHB Graphs with Cycle-Accurate Timing

We extend the  $\mu$ HB graph formalism from prior work [46], [55]–[59], [80], [82] with *cycle-accurate* timing information. In particular, *for all*  $\mu$ PATHs *in this paper* (except in Fig. 2a), a  $\mu$ HB node represents an instruction updating a particular set of state elements *in a specific cycle*, while an edge represents a *one-cycle* happens-before relationship. This extension enables  $\mu$ HB graphs to express that an instruction may update the same set of state elements in multiple (consecutive or nonconsecutive) cycles, which is needed to represent real designs, e.g., ones where an execution unit has variable latency (like CVA6-MUL in Fig. 1) or throughput (like CVA6-OP in Fig. 2).

Using our cycle-accurate  $\mu$ HB graph notation, the  $\mu$ PATHs in Figs. 2b and 2c depict distinct (concrete) executions of an ADD on CVA6-OP that distinguish when the ADD is packed or not, respectively. We use row label Row(n) to denote the n-th update to the set of state elements referred to by Row.

We use a special notation to summarize l consecutive updates to the same set of state elements. Specifically, a pair of row labels Row(1) and Row(l) denote the first and last (*l*-th) consecutive updates to the state elements referred to by Row. Node labels specify the value of l (which may be execution dependent) for a particular concrete  $\mu$ PATH. For example, in Fig. 2c, the node at ID(l) denotes an ADD's second consecutive update to the state elements referred to by ID. Dashed edges that relate a Row(1) node to its corresponding Row(l) node represent a totally ordered (by  $\mu$ HB edges) sequence of l - 2nodes, ordered after Row(1) and before Row(l), with no other outgoing edges. When l = 2 (as in Fig. 2c for ID(l)), the dashed edge represents a normal (solid)  $\mu$ HB edge.

In every  $\mu$ PATH in this paper—each of which was synthesized from CVA6 [100] using RTL2M $\mu$ PATH (or, in the case of Figs. 1 and 2, adapted from synthesized  $\mu$ PATHs)—IF represents the first set of state elements that an instruction updates upon being fetched, and scbCmt represents those updated upon commit. Thus, one can deduce that a set of state elements S (row label) is updated in cycle t of an instruction's execution, along some  $\mu$ PATH, if t is longest sequence of  $\mu$ HB edges from the node at IF to the node at S, accounting for implicit nodes and edges due to consecutive state updates. An instruction's overall latency is given by the longest sequence of  $\mu$ HB edges from the node at IF to the node at scbCmt, e.g., four (Fig. 2b) or five (Fig. 2c) cycles for a packed or non-packed ADD on CVA6-OP, respectively.

In summary, our cycle-accurate  $\mu$ PATH abstraction provides a precise accounting of an instruction's hardware resource usage (i.e., state updates) in time and space.

# C. Recognizing µHB Nodes with Performing Locations

RTL2M $\mu$ PATH uses static netlist analysis, linear temporal logic (LTL) [62], [72] property generation (from property templates), and model checking [15], [28] to uncover all  $\mu$ PATHs for each implemented instruction on a given SystemVerilog processor design (§V). Importantly, it requires that a model checker be able to recognize the various components of a  $\mu$ PATH— $\mu$ HB nodes and edges—when exploring instructions' executions. As one-cycle happens-before relationships, edges are readily expressible in LTL syntax. However, nodes must be explicitly conceptualized in terms of RTL signals.

Recall that a  $\mu$ HB node represents an instruction updating a particular set of design states in a given cycle (§III-B). Thus, a model checker recognizing a  $\mu$ HB node equates to it detecting what state elements are updated in some execution cycle and attributing these updates to a particular in-flight instruction. At first glance, this task appears highly challenging, given that modern processors execute numerous instructions concurrently and out-of-order. However, we observe that the same mechanisms that enable a processor to orchestrate instructions' write access to design states can also be leveraged by a model checker to recognize  $\mu$ HB nodes.

In particular, we find that a subset of finite state machines (FSMs) within a processor's control path, which we call *micro-op FSMs* ( $\mu$ FSMs), govern instructions' state updates throughout their execution, from the time they are fetched until possibly after they commit (e.g., when stores update cache state). A  $\mu$ FSM is a tuple (iir, vars), where iir is an instruction identifying register (IIR), which holds a unique instruction identifier (IID) for an in-flight instruction, and vars is a collection of state elements, which encode the  $\mu$ FSM's state variables. Example IIDs include program counters (PCs) [46], [73], reorder buffer (ROB) or scoreboard (SCB) identifiers, and memory transaction identifiers. An inflight instruction acquires a  $\mu$ FSM by placing one of its IIDs in the  $\mu$ FSM's iir, progresses through various  $\mu$ FSM states (i.e., concrete valuations of its vars), and then releases the  $\mu$ FSM (i.e., by setting its vars to an *idle* state). The valuation of a  $\mu$ FSM's vars in a given cycle grants the instruction whose IID is contained in its iir exclusive write access to a particular subset of design states.

| // store_unit.sv                                 |                    |

|--------------------------------------------------|--------------------|

| <pre>enum logic {} state_d, state_q;</pre>       | // vars0           |

| <pre>logic [TRANS_ID_BITS-1:0] trans_id_n,</pre> | trans_id_q;// iir0 |

| + logic [riscv::VLEN-1:0] st_pc_n, st_pc         | _q; // pcr0        |

| <pre>// load_store_unit.sv</pre>                 |                    |

| assign lsu_req_i = {                             |                    |

| lsu_valid_i, fu_data_i.trans_id,                 | // (vars1, iir1)   |

| + , pc_i };                                      | // pcrl            |

Fig. 3: Close proximity of  $\mu$ FSMs' iir and vars components (§III-C). PCRs are added (+) near IIRs that do not hold PCs (§V).

Leveraging  $\mu$ FSMs, we conceptualize  $\mu$ HB nodes in terms of RTL signals as follows. First, we define the notion of a performing location (PL)-similar to a pipeline stage, but more granular—as a  $\langle \mu fsm, state \rangle$  tuple, where  $\mu fsm$  is a  $\mu$ FSM (i.e., an (iir, vars) tuple), and state denotes a valid, non-idle valuation of  $\mu$ fsm's vars. Hence, the set of all PLs for a processor implementation denotes the set of all valid, non-idle states across all of the design's  $\mu$ FSMs. Next, we say that "an instruction *i visits* (i.e., occupies) PL  $\langle \mu fsm, state \rangle$  some cycle," if at the start of that cycle,  $\mu fsm$ 's iir contains an IID of i and  $\mu$ fsm's vars is set to state. Like a pipeline stage, a PL can be occupied by a single instruction at a time, whose state updates (which take effect at the start of the next cycle) it encapsulates. Unlike a pipeline stage, an instruction may visit multiple PLs in the same cycle. Finally, we direct a model checker to recognize a  $\mu$ HB node during an instruction's execution on a microarchitecture when it detects the instruction visiting a particular PL in a given cycle. Hence, in all  $\mu$ PATH figures in this paper, row labels (ignoring parentheticals) denote PLs.

We require the designer to identify all signals that comprise  $\mu$ FSMs (i.e., their IIR and state variable components) in the input design (§V-A). RTL2M $\mu$ PATH uses these signals to uncover all PLs for the design and then all ways in which they can be assembled into valid  $\mu$ PATHs for instructions. Specifying  $\mu$ FSMs turns out to be straightforward, since they are already in use to support functional verification efforts [42], [43]. Fig. 3 illustrates the close proximity of  $\mu$ FSMs' IIR and state variable signal definitions in CVA6 [100].

# IV. SYNTHLC APPROACH: APPLYING MULTI-µPATH SYNTHESIS TO HARDWARE SECURITY VERIFICATION

In designing RTL2M $\mu$ PATH, we make an important observation: an instruction that exhibits  $\mu$ PATH variability (>1  $\mu$ PATH) on some processor implementation strongly indicates the presence of a microarchitectural side channel in the design. Based on this observation, we develop SYNTHLC, the first automated approach and tool for formally verifying hardware adherence to microarchitectural leakage contracts (§II-B).

This section presents the SYNTHLC approach; a presentation of its implementation as a tool is deferred until §V. We first formalize instances of instruction  $\mu$ PATH variability using the notion of a *decision* (§IV-B). Second, we show how an instruction's decisions can be attributed to the outputs of *path selector functions* in the microarchitecture (§IV-C). If a path selector function output depends on some instruction's

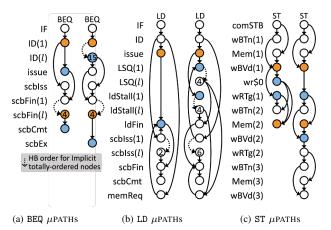

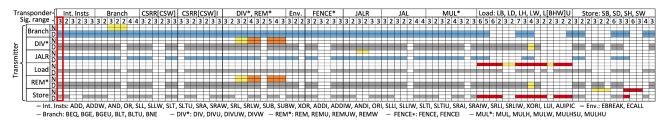

Fig. 4: A sampling of  $\mu$ PATHs for the CVA6 core (for BEQ, LD) and data cache (for ST), synthesized by RTL2M $\mu$ PATH (§VII). Row(1/l): 1st/l-th visit to Row. Node label: value of l for  $\mu$ PATH.

operands, it is a *leakage function*, and said instruction is a transmitter. Instructions whose decisions can be attributed to leakage functions are *transponders*. From leakage functions, we derive *leakage signatures*—a unifying formalism that captures all relevant features of six leakage contracts from prior work (summarized in §II-B and Table I), which are not already captured by  $\mu$ PATHs (§IV-D). SYNTHLC conducts leakage contract verification by synthesizing a comprehensive set of leakage signatures from processor RTL (§V).

We present the concepts above using a more complex illustrative example involving store-to-load stalling (§IV-A).

# A. Illustrative Example: Store-to-Load Stalling

Consider two  $\mu$ PATHs for a load (LD) executing on the RISC-V CVA6 CPU [100], shown in Fig. 4b. Following its visit to the issue PL (orange node), a LD exhibits one of two *decisions*. It stalls (right  $\mu$ PATH), progressing to LSQ and ldStall (blue nodes), if the page offset of its address operand matches that of any older pending store (ST) in the speculative or committed store buffers (STBs)—its *path selector function*. Else, it completes (left), progressing to ldFin (blue node).

Hardware side-channel defenses (§II-B) must ensure that stores (*transmitters*) do not leak their (private) address operands to a receiver who observes the  $\mu$ PATHs of executing loads (*transponders*), e.g., by timing their execution latency five or nine cycles for the left or right  $\mu$ PATH, respectively, in Fig. 4b. CT contracts would declare store address operands as unsafe for processing secrets. STT, SDO, and SPT would flag such a load as an implicit branch, while Dolma would categorize the load/store as inducive/resolvent micro-ops. OISA would specify that store address operands are unsafe or require hardware mechanisms avoid this channel for stores with secret operands. MI6 declares this sort of leakage as out-of-scope.

# B. Formalizing Instances of µPATH Variability with Decisions

We propose the notion of a *decision* to characterize specific variations across the different  $\mu$ PATHs of a particular instruc-

tion on a microarchitecture (e.g., a LD on CVA6).

Suppose  $\mu PATH_M^I$  is the set of all possible  $\mu PATHs$  that a dynamic instance of instruction I (e.g., I = LD) can exhibit when it runs on microarchitecture M. Informally, "a decision made by I on M" is a tuple (src, dst)—where src is a single decision source PL (or decision source) and dst is a set of decision destination PLs (or decision destinations)-that pinpoints a divergence between a pair of I's  $\mu$ PATHs on M. Orange/blue nodes in  $\mu$ HB graph figures throughout the paper denote some, but not all (for clarity of presentation), decision sources/destinations. Suppose  $\mathbf{d}_M^I$  is the set of all decisions that I can make on M. Then,  $(src, dst) \in d_M^I$  if and only if: For some  $p, p' \in \mu \text{PATH}_M^I$ , I visits src in p one cycle before it visits exactly the PLs in dst, and I visits src in p' one cycle before it visits a *different* set of PLs than exactly those in dst. By  $\operatorname{src}_M^I$  we denote the set of all decision sources across all of I's decisions on M.

For example, given the  $\mu$ PATHs in Figs. 2b and 2c, and considering the orange and blue colored nodes exclusively (for brevity), ADD has decision sources and decisions:

$$\begin{split} \mathbf{src}_{\mathrm{CVA6-OP}}^{\mathtt{ADD}} &= \Big\{\mathtt{ID}\Big\}\\ \mathbf{d}_{\mathrm{CVA6-OP}}^{\mathtt{ADD}} &= \Big\{(\mathtt{ID}, \{\mathtt{issue}, \mathtt{scblss}\}), (\mathtt{ID}, \{\mathtt{ID}\})\Big\}. \end{split}$$

Similarly, given Fig. 4b and considering only colored nodes, LD has decision sources and decisions:

$$\begin{split} \mathbf{src}_{\mathrm{CVA6}}^{\mathtt{LD}} &= \Big\{\mathtt{issue} \Big\} \\ \mathbf{d}_{\mathrm{CVA6}}^{\mathtt{LD}} &= \Big\{(\mathtt{issue}, \{\mathtt{ldFin}\}), (\mathtt{issue}, \{\mathtt{LSQ}, \mathtt{ldStall}\}) \Big\}. \end{split}$$

Note that in practice, decisions are defined with respect to PLs, irrespective of how many times they have been visited. For example, in Fig. 1, scblss is a decision source for MUL on CVA6-MUL; it may be followed by decision destinations {scblss,mulU}, {scblss}, or {scbCmt}.

# C. Selecting a Decision with a Path Selector Function

Suppose  $i_I$  is a dynamic instance of instruction I that visits decision source  $src \in src_M^I$  during its execution on microarchitecture M. Which decision  $i_I$  exhibits with respect to src—i.e., which decision destination(s)  $i_I$  visits one cycle after visiting src—is determined by a *path selector function* in hardware. In particular, during the cycle in which  $i_I$  visits src, a path selector function is queried to determine where  $i_I$ will progress to next. We use I\_src to denote a path selector function that is queried when an instruction of type I visits decision source src; it returns a set of decision destinations.

Fig. 5 shows example path selector functions for CVA6-OP and CVA6 [100]. Path selector functions may have *explicit inputs* that are provided in the function argument list and *implicit inputs* that are not. Explicit inputs are instructions whose operands appear in the function body, capturing how architectural state influences  $\mu$ PATH variability. Implicit inputs are accessed in the function body, capturing how microarchitectural state influences  $\mu$ PATH variability.

// CVA6-OP Core ADD ( $\S$ III-A): ADD (i.e., ADD<sup>N</sup>) in ID is issued if it is ready (the oldest in ID) or eligible for operand packing; else, it is stalled.  $\begin{array}{l} \texttt{dst ADD\_ID(ADD^N i0, ADD_D^D i1):} \\ \texttt{return ite}(((\texttt{visit(i1,ID)} \land (\forall \texttt{arg} \in \{\texttt{i0.arg0}, \texttt{i0.arg1}, \texttt{i1.arg0}, \texttt{i1.arg1} \\ \texttt{}, \texttt{msb}(\texttt{arg}) < \texttt{32})) \lor \texttt{rdy}(\texttt{i0}), \{\texttt{scblss}, \texttt{issue}\}, \{\texttt{ID}\}) \end{array}$ // CVA6 Core LD (§IV-A): LD in issue finishes or is stalled depending on whether its address page offset overlaps with that of a pending ST. dst LD\_issue(LD<sup>N</sup> i0, ST<mark>D</mark> i1):  $\mathsf{return} \ \mathsf{ite}((\mathsf{i1.addr} \in (\mathsf{comSTB} \cup \mathsf{specSTB}) \land$  $offset(i0.addr) == offset(i1.addr)), \{IdStall, LSQ\}, \{IdFin\})$ // CVA6 Cache ST (§VII-A2): A ST accesses one of two data banks on a hit in the 4-way set-assoc. no-write-alloc. cache. dst ST\_wBVId(ST<sup>N</sup> i0, LD<sup>S</sup> i1) :  $hit = (cacheTag[set(i1.addr)][way] == tag(i1.addr) \land set(i1.addr) \land set(i1.addr$ i0.addr) == set(i1.addr)  $\land$  tag(i0.addr) == tag(i1.addr)) return ite(hit,{wRTag,wr\$[way/2]},{wRTag}) // CVA6 Core ST (new channel, §VII-A1): ST at comSTB is stalled from draining to memory if its address offset does not match a younger LD.  $dst ST_comSTB(SW^N i0, LD_V^D i1)$  :  $return ite((visit(i1, issue) \land offset(i0.addr) == offset(i1.addr)),$ {memRq, comSTB}, {comSTB}})

Fig. 5: Leakage function examples. Implicit inputs and leakage signature components are highlighted.  $T^{\mathbb{N}}/T_{\mathbb{D}[Y}^{\mathbb{N}}/T^{\mathbb{S}}$ : intrinsic / older or younger dynamic / static transmitters. PO: program order. msb: most significant bit. ite(c,t,f): t if c is true; else, f.

Moreover, each explicit input to a leakage signature has a type that captures both its *instruction type* (opcode/function) and particular *runtime conditions* (encoded with N, D, or S superscripts and 0 or Y subscripts—detailed below) that must be satisfied for the leakage signature to be applicable. In particular, with respect to a dynamic instruction  $i_I$  of type (opcode/function) I that visits  $src \in src_M^I$  on microarchitecture M and queries path selector function  $I\_src$ , each explicit input  $i_T$  (an instruction with opcode/function T) is typed as:

- Intrinsic  $(T^{\mathbb{N}} i_T)$ , if  $i_I = i_T$ , i.e.,  $i_T$  is the instruction currently visiting src.

- <u>Dynamic</u>  $(T_{0|Y}^{\mathbb{D}} i_T)$ , if  $i_T$  is older (0) / younger (Y) than  $i_I$  (in program order), and  $i_T$  must be in-flight (visiting some PL) when  $i_I$  visits src for it to influence I\_src's output. Notably, when  $i_T$  is younger than  $i_I$ , M can be susceptible to speculative interference attacks [17].

- <u>Static</u>  $(T^{s} i_{T})$ , otherwise.

Illustrative Example: LD\_issue Path Selector Function: For our store-to-load stalling example (§IV-A), the path selector function LD\_issue in Fig. 5 is queried to select a decision for a dynamic LD instruction  $i_{LD}$  during any cycle in which it visits the issue PL. Its explicit inputs LD<sup>N</sup> i0 and ST<sup>D</sup><sub>0</sub> i1 indicate that  $i_{LD}$ 's decision at decision source issue is a function of its own operands and those of another older in-flight ST, respectively. Its outputs are one of two sets of destination PLs: {ldStall,LSQ} (stall  $\mu$ PATH) or {ldFin}. The function body shows that the output of LD\_issue specifically depends on the address operands of  $i_{LD} = i0$  and i1.

A receiver that can determine which  $\mu$ PATH  $i_{LD}$  exhibits relative to issue, learns LD\_issues's return value. Since the return value depends on the address operands of explicit inputs

| Defense                                            | Leakage Contract Components          |              | Leakage Sig.                   |              |                  |              |              |              |

|----------------------------------------------------|--------------------------------------|--------------|--------------------------------|--------------|------------------|--------------|--------------|--------------|

| Derense                                            | Leakage Contract Components          | $\mu$        | $\mu$ P src $T^{\mathbb{N}}$ 7 |              | $T^{\mathtt{D}}$ | $T^{S}$      | a            |              |

| CT, SCT (§II-B)<br>SpecShield [16]<br>ConTExt [76] | Constant-time contract (§II-B)       | -            | -                              | -            | ~                | ✓            | ~            | ~            |

| MI6 [20]                                           | Contention-based dynamic channels    | -            | $\checkmark$                   | $\checkmark$ | $\checkmark$     | $\checkmark$ | -            | -            |

|                                                    | Static channels                      | -            | $\checkmark$                   | $\checkmark$ | -                | -            | $\checkmark$ | -            |

| OISA [97]                                          | Input-dependent arithmetic units     | -            | -                              | $\checkmark$ | $\checkmark$     | -            | -            | $\checkmark$ |

|                                                    | Explicit channels                    | -            | $\checkmark$                   | $\checkmark$ | $\checkmark$     | -            | -            | $\checkmark$ |

| STT [99]<br>SDO [98]<br>SPT [26]                   | Implicit channels                    | -            | $\checkmark$                   | $\checkmark$ | -                | $\checkmark$ | $\checkmark$ | $\checkmark$ |

|                                                    | Implicit branches                    | -            | $\checkmark$                   | -            | -                | $\checkmark$ | $\checkmark$ | $\checkmark$ |

|                                                    | Prediction-based channels            | -            | $\checkmark$                   | $\checkmark$ | -                | -            | $\checkmark$ | $\checkmark$ |

|                                                    | Resolution-based channels            | -            | $\checkmark$                   | $\checkmark$ | -                | $\checkmark$ | -            | $\checkmark$ |

| SDO [98]                                           | Data-oblivious variants              | $\checkmark$ | -                              | -            | $\checkmark$     | -            | -            | $\checkmark$ |

|                                                    | Variable-time micro-ops              | -            | -                              | -            | $\checkmark$     | -            | -            | $\checkmark$ |

| Dolma [53]                                         | Contention-based dynamic channels    | -            | $\checkmark$                   | $\checkmark$ | $\checkmark$     | $\checkmark$ | -            | $\checkmark$ |

|                                                    | Inducive micro-ops                   |              | $\checkmark$                   | -            | -                | $\checkmark$ | -            | $\checkmark$ |

|                                                    | Resolvent micro-ops                  | -            | -                              | -            | -                | $\checkmark$ | -            | $\checkmark$ |

|                                                    | Prediction resolution points         | -            | $\checkmark$                   | $\checkmark$ | -                | $\checkmark$ | -            | $\checkmark$ |

|                                                    | Persistent state modifying micro-ops | -            | -                              | -            | -                | -            | $\checkmark$ | $\checkmark$ |

TABLE I: Six leakage contracts (§II-B) mapped onto  $\mu$ PATHS ( $\mu$ ) and leakage signatures. a: Arguments.  $\sqrt{-}$ : Relevant/irrelevant to the leakage contract component.

$i_{\rm LD} = i0$  and i1, such a receiver may infer their values.

Leakage Functions and Transponders: At least one operand of an explicit input to a path selector function may leak its value to a receiver that observes the function output. So, we call a path selector function with at least one explicit input a *leakage function*; explicit inputs are *transmitters*. A receiver observes a path selector function output as a  $\mu$ PATH decision of the instruction that queried it. We call an instruction whose perceived  $\mu$ PATH variability leaks transmitter operands a *transponder*, extending the telecommunications analogy for characterizing hardware side-channel attacks (§II-A).

To summarize, a leakage function dst  $P\_src(i_T, i_{T'}, ...)$  characterizes a microarchitectural side channel, mapping the operand space(s) of transmitters T, T', ... that modulate it onto the observation space of a receiver that observes it. Assuming a receiver that observes  $\mu$ PATHs of executing instructions, the observation space consists of the set of distinct decisions that *transponder* P may exhibit relative to decision source src.

*Formally Characterizing Channels:* Notably, leakage functions enable formally defining static versus dynamic channels and passive versus active attacks (§II-A).

We call a channel (leakage function) static iff it is modulated by a static transmitter. We call a channel dynamic iff it is modulated by an intrinsic or dynamic transmitter. A channel may be static *and* dynamic, e.g., consider a leakage function whose output decides whether or not a transponder LD stalls on a cache access. The decision may depend on another dynamic LD<sup>D</sup> that contends for the same read port *or* another static LD<sup>S</sup> that evicted LD's cache line, causing a cache miss. SYNTHLC discovers this scenario when analyzing the CVA6 cache (§VI).

By definition, a transmitter is an instruction in a victim program (II-A). In a passive attack, the transponder is a victim instruction, which the attacker passively monitors. In

an active attack, the transponder is a receiver instruction.

# D. Unifying Leakage Contracts with Leakage Signatures

We propose a unifying formalism, called a *leakage sig-nature*, to capture all relevant features of six state-of-the-art leakage contracts, summarized in §II-B, which are not already captured by  $\mu$ PATHs. A leakage signature is a leakage function that is restricted to the yellow-highlighted components of Fig. 5: transponder and decision source (function name), typed transmitters (explicit inputs), unsafe transmitter arguments (in the function body), and decision destinations (return values).

Table I shows how various components of the six leakage contracts in §II-B can be derived from  $\mu$ PATHS ( $\mu$ ) and leakage signatures. These contracts do not consider notions of decision destinations nor do they explicitly distinguish older versus younger dynamic transmitters, so the table omits these details.

Consider the five leakage contract components shared by STT [99], SDO [98], and SPT [26]. Each can be derived from the checked ( $\checkmark$ ) leakage signature components in Table I as follows. *Explicit channels* denote sources of  $\mu$ PATH variability (src) for intrinsic transmitters ( $T^{\mathbb{N}}$ ), which are transponders (P) by definition, as a function of their arguments (a). *Implicit channels* are sources of  $\mu$ PATH variability (src) for transponders (P) as a function of dynamic ( $T^{\mathbb{D}}$ ) or static ( $T^{\mathbb{S}}$ ) transmitters' arguments (a). *Implicit branches* are transponders (P) that exhibit  $\mu$ PATH variability due to dynamic ( $T^{\mathbb{D}}$ ) or static ( $T^{\mathbb{S}}$ ) transmitters' arguments (a). *Prediction-based channels* and *resolution-based channels* manifest as sources of  $\mu$ PATH variability (src) for transponders (P) due to dynamic ( $T^{\mathbb{D}}$ ) and static ( $T^{\mathbb{S}}$ ) transmitters' arguments (a), respectively.

# V. SYNTHLC TOOL: USING RTL2MµPATH TO SYNTHESIZE LEAKAGE SIGNATURES FROM PROCESSOR RTL

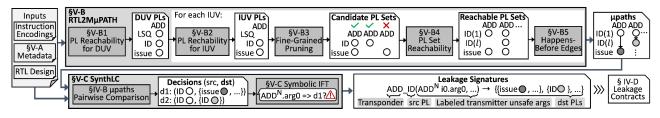

We present SYNTHLC, an automated approach and tool for synthesizing a comprehensive set of formally verified leakage signatures from a SystemVerilog processor design, from which one can derive the leakage contracts in Table I. First, SYNTHLC uses RTL2M $\mu$ PATH to uncover all  $\mu$ PATHs for each instruction implemented on the design (§V-B). Instructions with more than one  $\mu$ PATH are *candidate transponders*. Second, SYNTHLC uses a symbolic information flow analysis to classify each candidate transponder's decisions as dependent on the unsafe operand(s) of (typed) transmitter(s) or not (§V-C). The result is a set of true transponders with leakage signatures that characterize all of their transmitter operanddependent  $\mu$ PATH variability.

#### A. Inputs & Metadata Requirement

Both SYNTHLC and RTL2M $\mu$ PATH require three inputs: the SystemVerilog *design under verification* (DUV), a list of *encodings* for each implemented instruction, and design *metadata*. We detail our metadata requirement below, which follows from the fact that these tools make extensive use of model checkers to evaluate auto-generated LTL properties, formulated as SystemVerilog Assertions (SVAs) [2]. Table II quantifies this metadata for the CVA6 Core and Cache (§VI).

Fig. 6: RTL2MµPATH (top) and SYNTHLC (bottom) synthesize a complete set of formally-verified leakage signatures.

First, the designer must identify the *instruction fetch register* (IFR) [46], which holds fetched instruction encodings before they are supplied by the processor frontend to the backend. RTL2MµPATH uses the IFR to constrain the execution traces considered by a model checker, e.g., to those that feature some specific *instruction under verification* (IUV) [32], [46], [73].

RTL2M $\mu$ PATH uses a single IID to track an IUV as it progresses through various PLs during its execution on the DUV (§III-C)—its PC. Hence, RTL2M $\mu$ PATH requires each  $\mu$ FSM's IIR to be a *program counter register* (PCR) [32], [46], [73], which contains the PC of the instruction occupying it. PCRs may be present in the original DUV or added in parallel to the IIRs in the DUV solely for verification [32], [46], [73].<sup>2</sup> Fig. 3 shows an excerpt of two CVA6 design files where we add PCRs in parallel to existing IIRs.

Once the DUV is augmented (if necessary) with PCRs, RTL2M $\mu$ PATH requires the user to supply all  $\mu$ FSMs as tuples of signal names (pcr, vars) that denote their PCR and state variable components (§III-C). Plus, since RTL2M $\mu$ PATH considers invalid any PL ( $\mu$ fsm, state) where state = *idle*, the user is also required to supply each  $\mu$ fsm's *idle* state(s). For CVA6, there are 21 PCRs, and thus  $\mu$ FSMs, in total; we add 14 PCRs to the baseline design.

To detect when instructions commit,  $RTL2M\mu PATH$  requires the user to supply the DUV's commit signal.

Two final inputs support SYNTHLC's symbolic information flow analysis. First, the user must identify the *architectural register file* (ARF) and *architectural main memory* (AMEM) to block taint propagation between instruction outputs/inputs. Second, they must identify *operand registers*, located at the issue or register read stage, to enable taint introduction for transmitter operands.

#### B. RTL2MµPATH Tool: Synthesizing µPATHs from RTL

For each IUV, taken from the input list of instruction encodings, RTL2M $\mu$ PATH finds all of its  $\mu$ PATHs by using model checkers to explore its execution behavior in *all reachable contexts*, starting from a *valid reset state*, i.e., a hard processor reset, where *only* architectural state is symbolically initialized. All reachable contexts indicates that the IUV may be preceded/followed by an arbitrary number of valid instructions.

We explain RTL2M $\mu$ PATH's synthesis procedure below, as depicted in Fig. 6. Each step involves instantiating numerous

| Identified in CVA6 Core                        |     |          |            |      |          |       |        |       |          |         |            |  |

|------------------------------------------------|-----|----------|------------|------|----------|-------|--------|-------|----------|---------|------------|--|

|                                                |     |          | $\mu$ FSMs |      | SMs PCRs |       | commit |       |          |         | AMEM       |  |

| 1 reg                                          | 21  | (7) regs | 38         | regs | 21       | regs* | 1 wire |       | 2 regs   | 1 array | 1 array    |  |

| Added to Core Added to Cache Identified in CVA |     |          |            |      |          |       | n CVA6 | Cache |          |         |            |  |

| PC                                             | Rs  | SV       |            | PC   | Rs       | S     | V      | IIR   | s (PCRs) | PCRs    | $\mu$ FSMs |  |

| 14 r                                           | egs | 39 LoC   |            | 9 re | gs       | 74 I  | юC     | 9     | (0) regs | 9 regs* | 13 regs    |  |

TABLE II: User annotations required by SYNTHLC (§V-A) and all/some [31], [32], [36] of prior works (§VIII). \*: With added ones.  $\mu$ FSMs signals correspond to their state variables (§III-C).

SVA properties from templates. Important SVA syntax for understanding our templates includes the notions of **cover** and **assume** statements. A **cover** property directs a model checker to search for *any* execution trace that satisfies a given condition. A *reachable* outcome is returned when a trace is found. An *unreachable* outcome is a proof that no such trace exists. An *undetermined* outcome indicates that a satisfying trace cannot be found due to a timeout or resource constraints, but it *may* exist. We discuss implications of undetermined model checker outcomes in §VII-B4. SVA **assume** statements constrain the execution traces considered by a model checker to those that satisfy their specified condition when evaluating SVA properties (e.g., **cover** properties).

1) PL Reachability for DUV: For each  $\mu fsm = \langle pcr, vars \rangle$ (§III-C), RTL2M $\mu$ PATH enumerates its feasible PLs by considering all constant valuations of vars and excluding useridentified *idle* states. Then RTL2M $\mu$ PATH instantiates SVA properties to prune those PLs that are proven *unreachable* on the DUV by any instruction. The remaining **DUV PLs** are those PLs reachable by some IUV (i.e., some IUV can visit them). Our CVA6 case study has a total of 41 DUV PLs.

Next, RTL2MµPATH conducts several *IUV-specific* analyses. 2) *PL Reachability for IUV:* Like the first step, but conditioned on a specific IUV, RTL2MµPATH instantiates SVA properties to discard from consideration PLs that are proven *unreachable* by the IUV, producing a set of **IUV PLs**. For example, in Fig. 6, the LSQ PL is part of the set of DUV PLs, but not included in the set of IUV PLs for an ADD.

3) Fine-Grained Pruning: For an IUV, our first goal is to derive its **Reachable PL Sets**. A Reachable PL Set is a set of PLs that is *exclusively* visited in one of the IUV's executions, i.e., there exists an execution of the IUV that visits all of the PLs in the set and no others.

Deriving all Reachable PL Sets for an IUV, naïvely, requires asking a model checker to consider each element in the *power*

<sup>&</sup>lt;sup>2</sup>Such auxiliary state elements exist exclusively within the verification environment, and are removed prior to synthesis and fabrication.

set of the IUV PLs and deduce its reachability. RTL2M $\mu$ PATH prunes this power set in two ways using SVAs: it removes elements from the power set that contradict *dominates* and *exclusive* relationships between PLs. We say  $pl_0$  *dominates*  $pl_1$  iff all executions of the IUV that visit  $pl_0$  also visit  $pl_1$ . We say  $pl_0$  and  $pl_1$  are (mutually) *exclusive* iff there exists no execution of the IUV that visits both  $pl_0$  and  $pl_1$ .

RTL2MµPATH deduces dominates (exclusive) relationships by instantiating and evaluating the top (bottom) SVA property template below for each ordered (unordered) pair of IUV PLs. In all such listings in the paper, blue (brown) terms are template arguments (SystemVerilog or SVA keywords).

```

pl_0_dom_pl_1: cover (!pl_0_visited & pl_1_visited);

pl_0_excl_pl_1: cover (pl_0_visited & pl_1_visited);

```

An *unreachable* outcome for the top (bottom) property proves there exists no execution trace where the IUV visited  $pl_1$  but not  $pl_0$  (visited both), thus helping to prune PL Sets.

4) PL Set Reachability: For each Candidate PL Set that remains after pruning, RTL2M $\mu$ PATH instantiates this property:

A *reachable* outcome indicates an execution trace exists where, by the time the IUV has disappeared from the processor  $(!(pl_0 | ...))$ , it has visited exclusively PLs in the Candidate PL Set (cand\_pl\_set).

Next, RTL2M $\mu$ PATH iterates over the elements of each **Reachable PL Set** (discovered above) and uses SVAs to determine which constituent PLs may non-consecutively or consecutively be revisited (§III-B). Non-consecutively revisited PLs are simply marked as such. Consecutively revisited PLs are duplicated and tagged as representing the first/last consecutive visit, e.g., ID(1)/ID(*l*) in Fig. 4. Knowing *which* PLs may be non-consecutively or consecutively revisited is sufficient to place HB edges and uncover all *decisions* across an IUV's  $\mu$ PATHs—what SYNTHLC ultimately derives from RTL2M $\mu$ PATH's output (§IV-B). So, RTL2M $\mu$ PATH can be configured to avoid deducing the exact number of revisits per PL (e.g., all possible values of *l* for ID(*l*)).

5) Happens-Before Edges: RTL2M $\mu$ PATH extends each Reachable PL Set to a full  $\mu$ PATH by deriving a partial order on visited PLs. RTL2M $\mu$ PATH considers as candidate HB edges all ordered pairs of PLs that are connected via pure combinational logic in the DUV to capture *causal* happens-before relationships among visited PLs exclusively. Each candidate edge is evaluated for every Reachable PL Set using SVAs to determine if it constitutes a true HB relationship.

6) All Cycle-Accurate  $\mu$ PATHs: While not needed by SYNTHLC, RTL2M $\mu$ PATH can be configured to uncover: (i) for each IUV, for each PL that it may revisit, the set of *revisit cycle counts* for the PL that the IUV can exhibit across all of its executions, or (ii) all  $\mu$ PATHs that concretize the precise number of visits to each revisited PL (as in Fig. 1, 4, 2b, and 2c). We direct RTL2M $\mu$ PATH to perform (i) for

Fig. 7: Constraints on SVA properties to classify transmitters as (1) intrinsic, (2a/b) older/younger dynamic, or (3) static.

CVA6 to support SDO (Table I). RTL2M $\mu$ PATH is currently not optimized for (ii), which generates *many* (still easy-tocheck) properties, proportional to the cross product of distinct concrete values per PL derived in (i). We expect we can drastically prune these properties (as in §V-B3), but it is unnecessary for our focus: leakage contract verification.

#### C. Attributing µPATH Variability to Transmitters

After RTL2M $\mu$ PATH uncovers all  $\mu$ PATHs for each implemented instruction on the DUV, SYNTHLC identifies candidate transponders and collects all decisions for each (§IV-B).

1) Symbolic IFT: For each candidate transponder P, SYNTHLC considers each of its decisions  $(src, dst) \in d_M^P$ (M is the DUV) in turn to determine if P exhibits (src, dst)as a function of some transmitter T's unsafe operand op. All possible (T, op) pairs are considered for each decision.

To do this, SYNTHLC first augments the DUV with celllevel *information-flow tracking* (IFT) circuitry, which supports per-data-bit introduction and propagation of *taint* to track the explicit and implicit flows of certain data dynamically at runtime [78]. Next, it uses a model checker to consider a dynamic instance of P,  $i_P$ , and a dynamic instance of T,  $i_T$ , executing together in all reachable contexts following a valid reset state (§V-B), subject to three assumptions (Fig. 7). In all cases, each data bit is assigned one taint bit, taint is introduced for op of  $i_T$  exclusively, and taint is prohibited from propagating architecturally between instruction outputs/inputs.

Assumption 1 determines if T is an intrinsic transmitter with respect to (src, dst) by constraining  $i_T$  and  $i_P$  to be the same dynamic instruction. Assumption 2, which is composed of sub-assumptions 2a and 2b, determines if T is a dynamic transmitter by constraining  $i_T$  to be in-flight when  $i_P$  visits its decision source src. Sub-assumption 2a/2b considers the case where  $i_T$  is fetched before/after  $i_P$  (i.e.,  $i_T$  is older/younger than  $i_P$ ). Assumption 3 determines if T is a static transmitter by constraining  $i_T$  to have materialized and dematerialized in M before  $i_P$  reaches src.

Note that the third assumption uses one additional taint bit per data bit to support flushing "sticky" taint that is associated with op's dynamic influence on transponders'  $\mu$ PATHs, thereby considering its static influence exclusively.

The SVA template below has two **assumes**. The first one introduces taint (exclusively) at the register corresponding to op (§V-A), when  $i_T$  is at the issue stage. The second restricts execution traces to those satisfying one of three aforementioned assumptions. The **cover** property searches for an execution trace where  $i_P$  visits src ( $src_pl$ ) once cycle before (##1) it visits all of the PLs in dst (( $dst_pl_0 \& \dots$ )) and the  $\mu$ FSMs of these decision destinations are tainted—signaling a dependence on  $i_T$ 's operand op.

```

// Candidate transponder decision (src_pl, {dst_pl_0, ...})

assume ((iT_at_issue) ^ (op_reg_taint == 1));

assume (assumption 1/2/3);

decision_taint: cover (src_pl ##1 ((dst_pl_0 & ...) &

(dst_pl_0_taint | ... )));

```

A *reachable* outcome results in assigning a *tag* to *P*'s decision (src, dst), denoting that it is dependent on typed (intrinsic / older or younger dynamic / static) transmitter *T*'s unsafe operand *op*. An *unreachable* outcome assign no tag.

After using the property above to evaluate every one of P's decisions (under all three assumptions, for every possible (I, op) pair), we can construct a leakage signature for each of P's decision sources as follows (§IV-D). If P exhibits at least two transmitter operand-dependent decisions with respect to  $src \in \mathbf{src}_M^P$ , we construct a leakage signature corresponding to leakage function P\_src (function name).<sup>3</sup> Examining tags assigned to all such decisions (those involving src) gives us typed transmitters (explicit inputs) and unsafe transmitter arguments (in the function body). Decision destinations (return values) are all sets of PLs dst such that  $(src, dst) \in \mathbf{d}_M^P$ .

Notably, SYNTHLC's symbolic IFT step also uncovers implicit inputs (Fig. 5) to leakage functions, which may be useful towards implementing the hardware side-channel defenses in §II-B using the leakage contracts in Table I.

2) Security Argument: A proof in our repository [1] shows that SYNTHLC produces a set of leakage signatures that capture all violations of hardware side-channel safety, as defined below, subject to a receiver  $R_{\mu PATH}$ .  $R_{\mu PATH}$  observes the PLs occupied by in-flight instructions in each cycle, modeling a receiver that perceives channel modulations via their impact on instruction/program execution time or resource contention.

**Definition V.1** (Hardware Side-Channel Safe). A microarchitecture M is *hardware side-channel safe* with respect to receiver R, or SC-Safe(M, R), iff:

$$\forall p. \forall \pi. \forall \sigma, \sigma'. \forall \mu. ArchCtrl(p) \Longrightarrow$$

$$(\sigma \approx_{\pi} \sigma' \implies O_R(\{p\}_M^{\langle \sigma, \mu \rangle}) = O_R(\{p\}_M^{\langle \sigma', \mu \rangle}))$$

(V.1)

Eq. V.1 quantifies over all programs p and security policies  $\pi$  (which label program inputs as public or secret), all pairs of initial architectural states  $\sigma$ ,  $\sigma'$  and all initial microarchitectural states  $\mu$ . Looking at the second line, the antecedent,  $\sigma \approx_{\pi} \sigma'$ , checks that the initial architectural states are *low-equivalent* with respect to  $\pi$ : they agree on the values of low data in  $\pi$ , i.e., p's public data inputs. The consequent,  $O_R(\{p\}_M^{\langle\sigma,\mu\rangle}) = O_R(\{p\}_M^{\langle\sigma',\mu\rangle})$ , asserts that R obtains identical observation traces when p runs on microarchitecture M from initial states  $\langle\sigma,\mu\rangle$  and  $\langle\sigma',\mu\rangle$ . Given our focus on *microarchitectural* (not architectural) side channels, the first line requires p to feature the same sequence of instructions along all branches of secret-dependent control-flow instructions (ArchCtrl(p)).

Eq. V.1 violations indicate that the observation trace obtained by receiver R from running program p with privacy policy  $\pi$  on microarchitecture M is *indisputably* a function of *p*'s high inputs. Note that secret-dependent control-flow instructions can still behave as microarchitectural transmitters and cause Eq. V.1 violations, e.g., if they create operand-dependent squashes. Moreover, virtually all microarchitecture, for any realistic receiver, will trigger Eq. V.1 violations—the goal of a leakage contract is to account for them all.

## VI. SYNTHESIZING LEAKAGE SIGNATURES FROM CVA6

We use SYNTHLC to synthesize leakage signatures from the RISC-V CVA6 CPU (commit #00236BE), considering all 72 instructions in the RV64I ISA and M extension (**RV64IM**).

CVA6 [100] is a 64-bit, 6-stage, single-issue RISC-V core featuring speculation and limited out-of-order write-back with diverse functional units (ALU, LSU, Mul/Div, CSR buffer). It has a FIFO scoreboard (SCB) that tracks instructions from issue to commit and retires instructions in-order. Functional units may complete out-of-order in the SCB provided older, non-retired instructions' destination registers do not match.

We configure the design as follows. Both speculative and committed store buffers (STBs) are sized to two entries. The SCB is sized to four entries, but due to a bug in CVA6 that we discovered during our case study, only three entries are ever occupied at a time by active instructions (§VII). Such downscaling is typical in formal verification [33], [34]. We configure CVA6 without a memory management unit, and our main experiment instantiates the CVA6 Core as the DUV. Another experiment instantiates the CVA6 Cache (L1 data cache and cache controller) as the DUV. CVA6 does not come with a Verilog behavioral model of memory, so we add a single-port RAM behavioral model consisting of 32 64-bit words for the CVA6 Core DUV; the load-store unit (LSU) and committed STB are modified to directly interface with memory.

The elaboration step black-boxes the design's frontend, since RTL2M $\mu$ PATH drives all issued instructions at the IFR with a model checker. The multiplier is also black-boxed to reduce verification complexity. Since RTL2M $\mu$ PATH explores control state behavior, purely combinational logic circuits can be safely abstracted—*a key benefit*. The core design features 8,577 lines of SystemVerilog; after elaboration there are 22,138 wires, 19,575 standard cells, 482 registers (11,985 D flip-flop bits), and 3 memory arrays (including ARF and AMEM in Table II). The data-cache is 4-way, 128B (scaled down from 32 KB), featuring 2,279 lines of SystemVerilog.

We supply required metadata from §V-A to RTL2M $\mu$ PATH and SYNTHLC (Table II). Our implementations of both tools use SVA 2009 [2] and the JasperGold v21.03 property verifier [22]. We use Verific [13] and Yosys [92] to parse SystemVerilog and instrument the DUV with IFT logic using CellIFT [78]. All experiments are run on three compute nodes, each of which features two 32-core 2.9GHz Intel Xeon CPUs with 512GB RAM.

#### VII. RESULTS & DISCUSSION

SYNTHLC synthesizes a complete set of leakage signatures for the CVA6 Core (considering all instructions), and a partial set for the CVA6 Cache (considering loads and stores).

$<sup>^{3}</sup>$ A single decision may be tagged transmitter operand-dependent due to imprecision of symbolic IFT (§V-C). At least two decisions must be operand-dependent to yield >1 receiver observations as a function of operand values.

Fig. 8: SYNTHLC CVA6 Core results. Transponders (coarse-grained columns) and their leakage signatures with output range sizes (finegrained columns), plus explicit inputs from intrinsic/dynamic transmitters in N/D-labeled rows, where the top/bottom sub-row is rs1/rs2. We distinguish secondary leakage (§VII-A1) and false-positive leakage (§VII-B1) from primary leakage (§VII). Primary leakage is categorized as involving explicit channels, or explicit branches using STT [99] terminology.

#### A. Summary of Results

We first discuss the transmitters and transponders surfaced by SYNTHLC in our experiments.

1) Transponders and Transmitters: CVA6 Core: Fig. 8 summarizes SYNTHLC's synthesis results for the CVA6 Core. Coarse-grained row/column types denote transmitters/transponders. Fine-grained row and column labels, respectively, denote transmitter types (intrinsic/dynamic) and ranges for distinct leakage signatures. The top/bottom sub-row for each fine-grained row indicates transmitter operand rs1/rs2.

SYNTHLC finds transponders and leakage signatures per V. We observe that (i) classes of transponders feature identical leakage signatures, and (ii) classes of transmitters are explicit inputs to the same leakage signatures where they feature identical types. So, Fig. 8 groups transponders and transmitters accordingly. Each fine-grained column represents a leakage signature P\_src, where P can be any transponder in the class represented by the coarse-grained column label. Colored cells within a column indicate P\_src's explicit inputs having intrinsic/dynamic transmitters on N/D crossing rows.

As an example, consider the leftmost fine-grained column, outlined in red. It corresponds to a leakage signature ADD\_ID that SYNTHLC synthesizes for ADD transponders on the CVA6 CPU. ADD\_ID may output one of three decisions for ADDs with respect to decision source ID. The top-/bottom-most colored cell in the column indicates that operand rs1 of a dynamic branch/store is an explicit input to ADD\_ID. Overall, this column indicates that an ADD exhibits three-way  $\mu$ PATH variability at ID as a function of dynamic branch/division/remainder operands (both rs1 and rs2), load/store operands (rs1, the base address), and JALR operands (rs1, the target address).

Colored Fig. 8 cells represent primary (orange, red, blue) versus secondary (gray) leakage. Primary/secondary leakage indicates that the transponder (column) can/cannot leak the transmitter's (row) unsafe operand without the presence of other transponders. Secondary leakage often arises due to shared resources, e.g., an ADD that is stalled from committing at the SCB, stuck behind an intrinsic transmitter (e.g., DIV).

SYNTHLC flags all 72 evaluated instructions as transponders and finds that the CVA6 core features intrinsic and dynamic transmitters exclusively (hence the omission of static transmitter labels in Fig. 8). **Nineteen** intrinsic transmitters are found: eight division (DIV) and remainder (REM) variants, seven load (LD) variants, and four store (ST) variants. **Twentysix** dynamic transmitters are found: all intrinsic transmitters plus six branch variants and JALR. Notably, all intrinsic transmitters except stores can exhibit execution time variability as a function of their operands. The paragraphs below summarize key findings, organized around classes of transponders.

*Load:* On CVA6, a LD transponder may exhibit several decisions at issue, including proceeding to destinations  $\{ldFin\}/\{LSQ, ldStall\}$  as described in \$IV-A as a function of rs1 of the LD itself (LD<sup>N</sup>) and rs1 of a dynamic store (ST<sup>D</sup><sub>D</sub>).

Store: A ST transponder exhibits  $\mu$ PATH variability following a PL in the committed STB (comSTB), where it stalls if a *younger* in-flight load with a different address is ready to access the single-R/W-port memory; CVA6 prioritizes serving the younger load. The leakage signature (ST\_comSTB in Fig. 5) output depends on rs1 of the ST itself (ST<sup>N</sup>) and rs1 of a dynamic load (LD<sup>P</sup><sub>Y</sub>). We are the first to uncover this channel when conducting CV6 leakage contract verification [31], [32].

Interestingly, this channel renders CVA6 susceptible to a *new* class of speculative interference attacks [17], involving *transient dynamic transmitters* (LDs, in the shadow of older excepting instructions) that create  $\mu$ PATH variability for older, *committed* transponders (STs). Since this  $\mu$ PATH variability takes place after STs commit, it does not impact their execution time. Classic variants [17] involve *transient intrinsic transmitters* whose own  $\mu$ PATH variability creates timing-differentiable  $\mu$ PATH variability for older, *bound-to-commit* transponders. Using transponders, we can more generally define speculative interference attacks as involving transient transmitters that create  $\mu$ PATH variability for older non-transient transponders.

*Division/Remainder:* SYNTHLC flags all DIV/REM variants as intrinsic transmitters, and thus, transponders. Both use serial division circuitry, taking one to sixty-six cycles to compute their results (based on revisit cycle counts, §V-B6).